近日,上海交大电子信息与电气工程学院微纳电子学系教授毛志刚、教授何卫锋团队在集成电路设计领域的国际顶级期刊《IEEE固态电路杂志》(IEEE Journal of Solid-State Circuits,简称JSSC)上连续发表两篇学术成果。

集成电路发展的主要方式是通过缩减晶体管尺寸来提高性能和集成度,同时降低功耗和制造成本。随着5 nm及以下节点CMOS技术逐渐应用于商用超大规模集成电路中,硅基晶体管的继续微缩面临着来自功耗、成本甚至是物理极限的限制。为了继续推进集成电路的发展,学术界和工业界对未来电子学的核心材料、器件结构以及系统架构进行了广泛探索和深入研究。

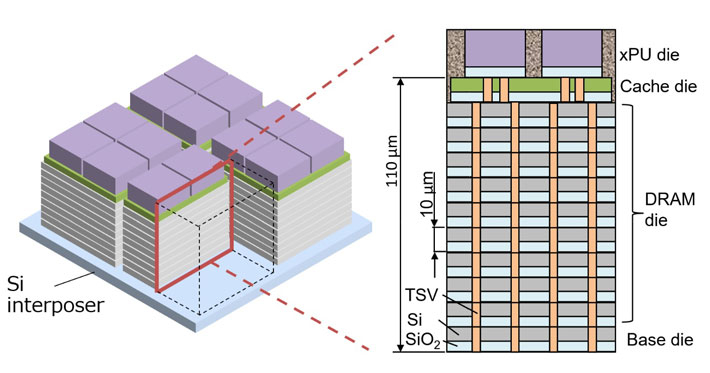

东京工业大学的研究人员报告称,一种处理单元和存储器的三维集成技术实现了全世界最高的性能,为更快、更高效的计算铺平了道路。这种名为“BBCube 3D”的创新堆叠架构实现了比最先进的存储器技术更高的数据带宽,同时也最大限度地减少了位访问所需的能量。

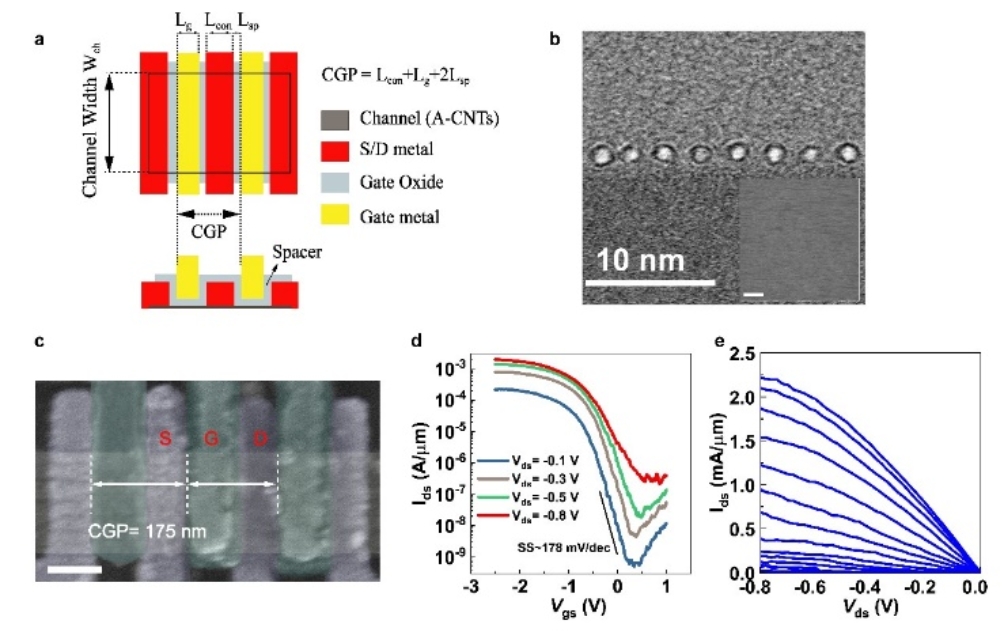

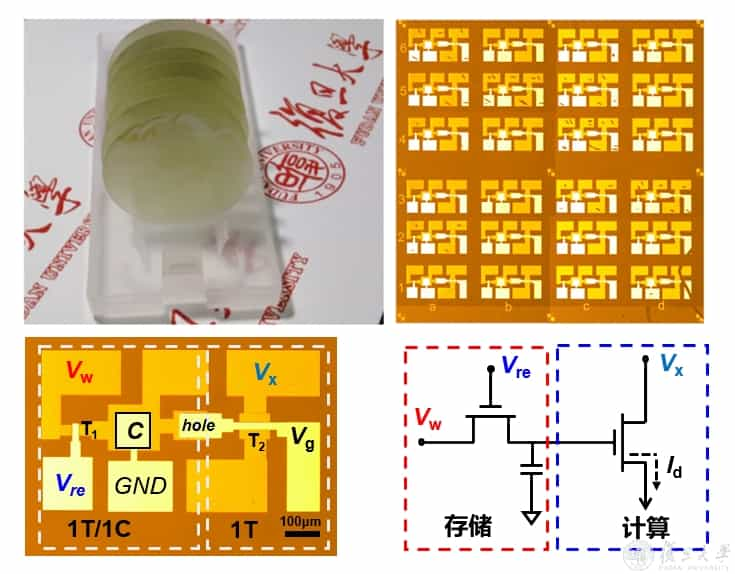

传统集成电路技术使用平面展开的电子型和空穴型晶体管形成互补结构,从而获得高性能计算能力。其密度的提高主要通过缩小单元晶体管的尺寸来实现。例如7nm节点以下业界使用极紫外光刻技术实现高精度尺寸微缩。极紫外光刻设备复杂,在现有技术节点下能够大幅提升集成密度的三维叠层互补晶体管(CFET) 技术价值凸显。然而,全硅基CFET的工艺复杂度高且性能在复杂工艺环境下退化严重。因此,研发与我国主流技术高度兼容的CFET器件与集成,对于自主发展新型集成电路技术具有重要意义。

美国哈佛大学科学家在最新一期《自然·电子学》杂志上撰文指出,他们首次展示了如何利用电场,在芯片上控制和调制声波,朝最终研制出声学集成电路又近了一步。

人工智能和可移动终端的迅猛发展,导致对芯片高算力和低能耗的要求越来越高。而目前集成电路最先进的晶体管沟道长度和厚度开始逐步接近原子尺度,而传统半导体材料已经接近性能极限。

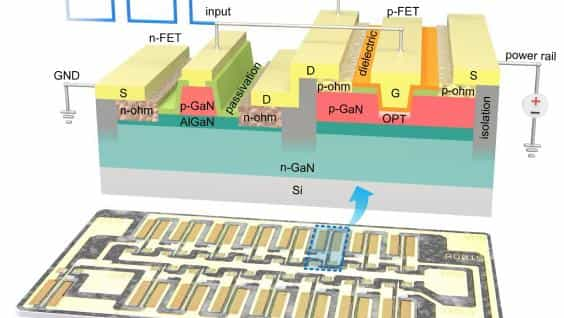

香港科技大学(科大)电子与计算机工程学系陈敬教授带领其团队,为方兴未艾的氮化镓(GaN)电子学研究引入重要的新成员——互补型逻辑电路。相关技术的成功实现大幅拓展了相关研究领域的疆界,有望使氮化镓基电子器件及相关集成电路的功能与性能得到进一步提升,从而更具竞争力。

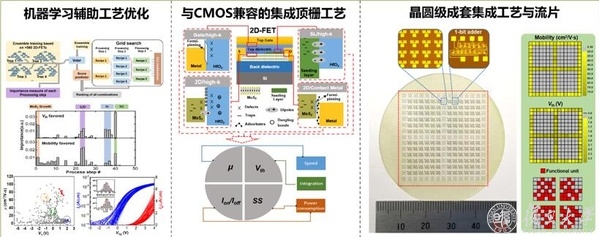

集成电路技术发展已经进入后摩尔时代,具有原子级厚度的新型二维半导体材料已受到了半导体机构与企业关注,并被认为将在下一代集成电路中发挥重要作用。目前产业应用主要的困难聚焦于晶圆级二维材料的获得和集成电路工艺的开发。