近日,上海交大电子信息与电气工程学院微纳电子学系教授毛志刚、教授何卫锋团队在集成电路设计领域的国际顶级期刊《IEEE固态电路杂志》(IEEE Journal of Solid-State Circuits,简称JSSC)上连续发表两篇学术成果。

集成电路发展的主要方式是通过缩减晶体管尺寸来提高性能和集成度,同时降低功耗和制造成本。随着5 nm及以下节点CMOS技术逐渐应用于商用超大规模集成电路中,硅基晶体管的继续微缩面临着来自功耗、成本甚至是物理极限的限制。为了继续推进集成电路的发展,学术界和工业界对未来电子学的核心材料、器件结构以及系统架构进行了广泛探索和深入研究。

传统集成电路技术使用平面展开的电子型和空穴型晶体管形成互补结构,从而获得高性能计算能力。其密度的提高主要通过缩小单元晶体管的尺寸来实现。例如7nm节点以下业界使用极紫外光刻技术实现高精度尺寸微缩。极紫外光刻设备复杂,在现有技术节点下能够大幅提升集成密度的三维叠层互补晶体管(CFET) 技术价值凸显。然而,全硅基CFET的工艺复杂度高且性能在复杂工艺环境下退化严重。因此,研发与我国主流技术高度兼容的CFET器件与集成,对于自主发展新型集成电路技术具有重要意义。

在过去几年的研究中,我主要聚焦在用新材料创造发明新的电子器件和系统。硅目前是集成电路的主要载体,但是遇到了挑战和极限,复旦团队探索3纳米新型芯片技术,多项成果有望用于集成电路产业

人工智能和可移动终端的迅猛发展,导致对芯片高算力和低能耗的要求越来越高。而目前集成电路最先进的晶体管沟道长度和厚度开始逐步接近原子尺度,而传统半导体材料已经接近性能极限。

近日,由清华大学机械系路新春教授带领清华大学成果转化项目公司华海清科研发的首台12英寸超精密晶圆减薄机(Versatile-GP300)正式出机,发往国内某集成电路龙头企业。该装备是路新春教授团队与华海清科股份有限公司(以下简称“华海清科”)继解决我国集成电路抛光装备“卡脖子”问题后的又一突破性成果,将应用于3D IC制造、先进封装等芯片制造大生产线,满足12英寸晶圆超精密减薄工艺需求。

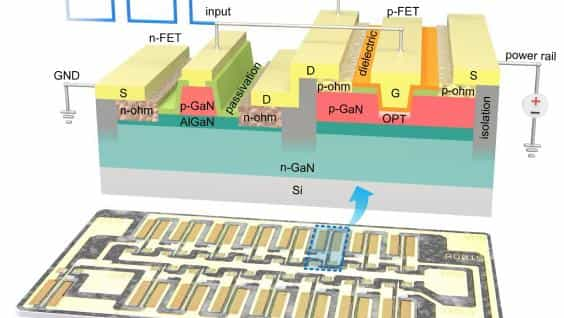

香港科技大学(科大)电子与计算机工程学系陈敬教授带领其团队,为方兴未艾的氮化镓(GaN)电子学研究引入重要的新成员——互补型逻辑电路。相关技术的成功实现大幅拓展了相关研究领域的疆界,有望使氮化镓基电子器件及相关集成电路的功能与性能得到进一步提升,从而更具竞争力。

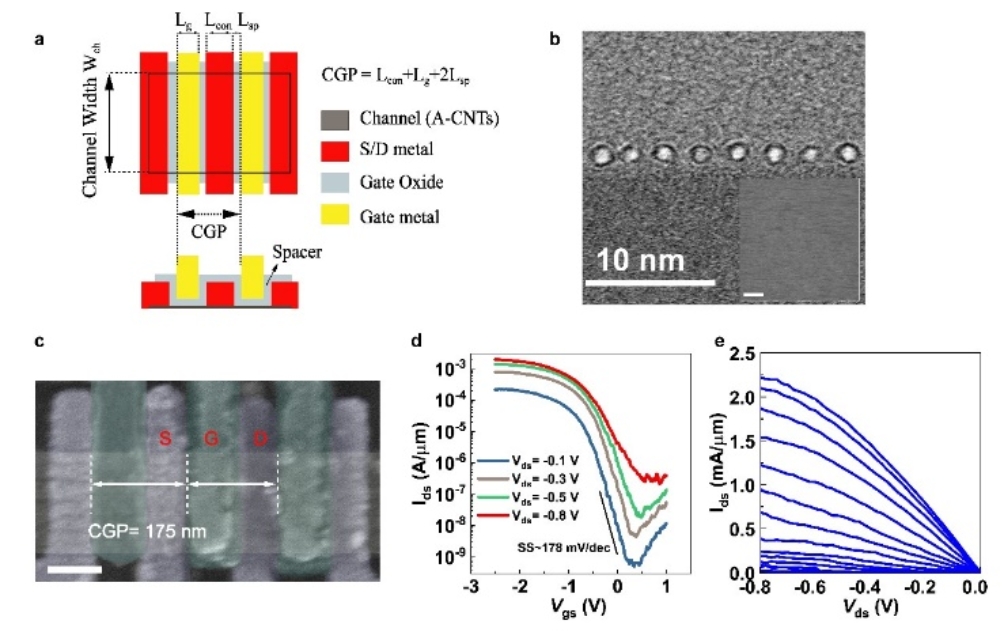

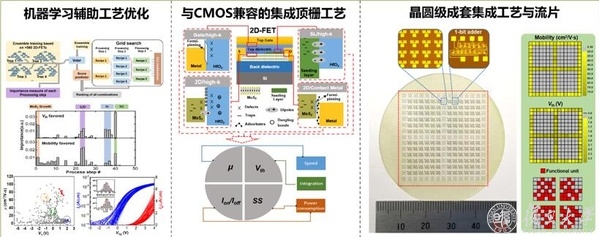

复旦大学微电子学院周鹏教授团队针对当下系统存算分离的能效瓶颈难题,发现了新型二维铁电半导体在集成电路领域的应用方案,实现了铁电存储计算技术的原始创新,提供了发展存算融合系统的器件范式。

氮化镓(GaN)是一种宽禁带半导体,第三代半导体的典型代表。与第一代半导体硅基的器件相比,GaN器件具有更高耐压、更快开关频率、更小导通电阻等特性,在功率电子器件领域得到广泛应用。相关研究显示,GaN器件适用于68%的功率器件市场;在功率转换电路中应用GaN器件可消除整流器在进行交直流转换时90%的能量损失,极大提高了能源利用效率;可使笔记本等电源适配器的体积缩小,减小设备体积,提高集成度。

超越摩尔定律(More than Moore)近几年来在世界级半导体元件会议上占有极重要的研究地位,晶体管尺寸的缩小将面临物理极限的考验,而积层型三维集成电路(monolithic 3DIC)即是其中解决问题最重要的工程技术之一,台湾半导体研究中心(Taiwan Semiconductor Research Institute, TSRI)自2010年开始研究相关技术,是开发前瞻物联网芯片与人工智能芯片的关键技术。

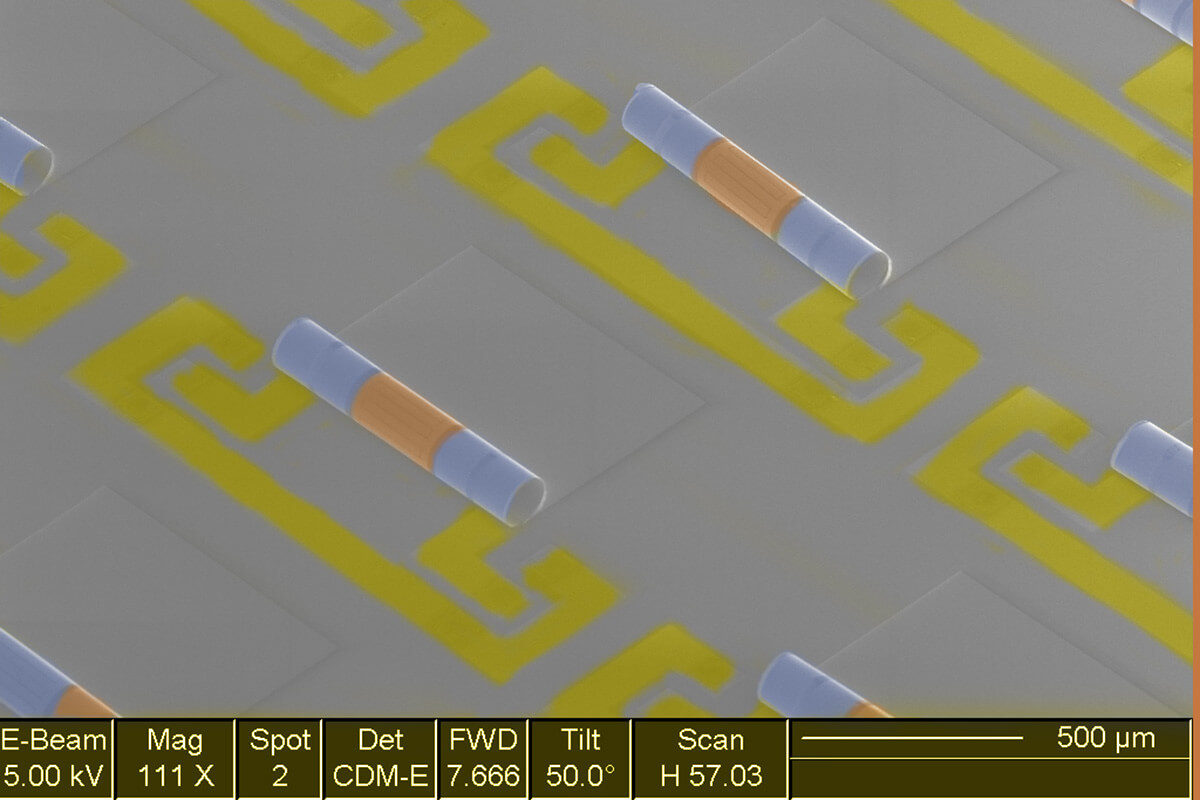

美国伊利诺伊大学香槟分校研究人员提出一种新型滤波器设计,通过集成电子滤波器元件,可将计算机芯片尺寸缩小10倍。研究人员放弃了传统的2D芯片的分布式滤波器网络设计,使用一个节省空间的3D卷式膜将滤波器的各个元件集成到单个组件中,随后将多层膜堆叠形成芯片组件。该滤波器适用于1-10 GHz频率范围的应用,并有望进一步拓宽频谱,应用于多种集成电路中。

近日,北京大学化学与分子工程学院彭海琳教授课题组首次报道高迁移率二维半导体表面氧化成高κ栅介质并应用于高性能场效应晶体管器件和逻辑门电路,该研究工作突破了二维高迁移率半导体器件与超薄介电层集成这一瓶颈,有望推动二维集成电路的发展。

随着摩尔定律接近极限,传统的晶体管器件已进入发展瓶颈。如何利用新原理、新结构和新材料来解决和优化传统半导体器件中的尺寸微缩和能耗等问题,是后摩尔时代半导体技术的发展重点。南京大学电子工程学院的王肖沐、施毅课题组同浙江大学的徐杨课题组以及北京计算科学研究中心合作,研制了一种在常温下实现能谷自旋流产生、传输、探测和调控等全信息处理功能的固态量子器件,成果近日发表在《自然·纳米技术》杂志上。