在21世纪的科技浪潮中,半导体技术的进步不断推动着信息时代的发展。特别是在内存处理器领域,全球的研究团队正在探索更高效、节能的新材料和技术。这种探索不仅对增强计算能力至关重要,也是实现更小型、更灵活电子设备的关键。近年来,二维材料因其独特的物理特性受到研究者的广泛关注。特别是二硫化钼,这种材料以其超薄、高导电性和机械稳定性,被视为微电子技术的革命性突破。

美国加州大学洛杉矶分校的研究人员已经成功开发出一种稳定的全固态热晶体管,这一成果有望改善计算机芯片的热管理效果。该热晶体管利用原子界面上电荷动力学的场效应,通过电场的开关来控制热运动。以下是该研究的一些关键发现和应用前景:

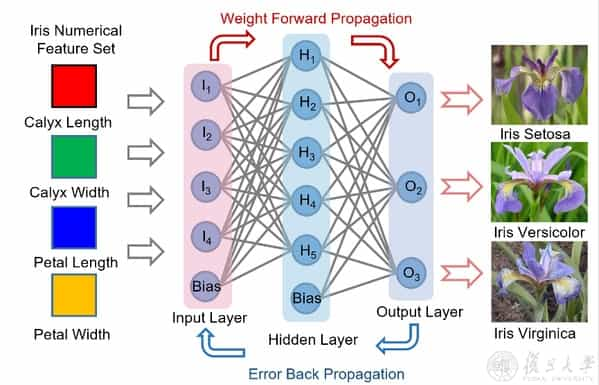

人工智能机器学习需要在数据中心支撑的云端完成,因为其计算需求巨大且耗能。然而,美国西北大学的研究人员开发出一种新型微晶体管,其能效比现有技术高出100倍,有望为移动和可穿戴设备带来新的智能水平。这种新型纳米电子设备可以在本地进行实时检测和数据处理,从而更迅速地干预健康紧急情况。

华中科技大学的翟天佑团队在二维高性能浮栅晶体管存储器方面取得了重要进展。他们研制出一种具有边缘接触特征的新型二维浮栅晶体管器件,其擦写速度和循环寿命等关键性能较现有商业闪存器件有所提升。相关研究成果近日发表于《自然-通讯》。

美国麻省理工学院一个跨学科团队开发出一种低温生长工艺,可直接在硅芯片上有效且高效地“生长”二维(2D)过渡金属二硫化物(TMD)材料层,以实现更密集的集成。这项技术可能会让芯片密度更高、功能更强大。相关论文发表在最新一期《自然·纳米技术》杂志上。

尽管木材是一种绝缘材料,但以前已经使用导电材料对其进行了改造,用于电池、超级电容器和其他电气系统。尽管其各种用途表明木材在能源和电子技术方面具有巨大潜力,但显然没有记录表明曾经用木材制造出电子晶体管。

日本科学家开发出首个固态电化学热晶体管,其能用电来管理热。新问世的固态热晶体管的效率可与目前广泛使用的液态热晶体管相媲美,且更稳定。相关研究刊发于21日出版的《先进功能材料》杂志。

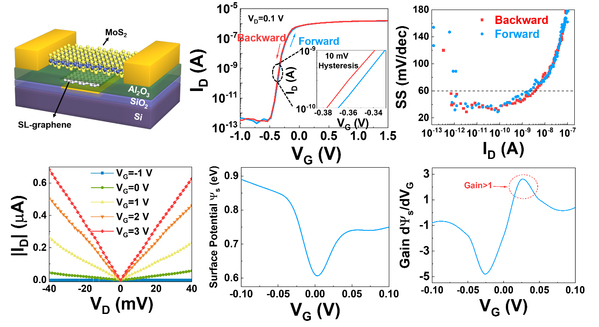

当前MOSFET器件的持续微缩所带来的功耗问题已经成为制约集成电路发展的主要瓶颈。研发新原理器件以突破MOSFET亚阈值摆幅(SS)为60 mV/dec的室温极限,是实现高速度、低功耗CMOS技术和集成电路的重要途径。近年来,包括隧穿晶体管(TFET)、负电容晶体管(NCFET)、冷源晶体管(CSFET)等在内的多种器件技术为实现陡峭亚阈值摆幅和低功耗器件性能提供了思路。

通过铁电栅极绝缘体和原子层沉积氧化物半导体通道,日本科学家制造了三维垂直场效应晶体管,可用来生产高密度数据存储器件。此外,通过使用反铁电体代替铁电体,他们发现擦除数据只需要很小的净电荷,从而提高了写入的效率。发表在2022年IEEE硅纳米电子研讨会上的该项成果,将催生新的更小、更环保的数据存储器。

基于钙钛矿的晶体管通过将具有空穴迁移率的p型半导体与n型半导体结合来控制电流。与迄今为止积极研究的n型半导体相比,制造高性能 p型半导体一直是一个挑战。POSTECH研究团队使用钙钛矿开发世界性能最高的p型晶体管

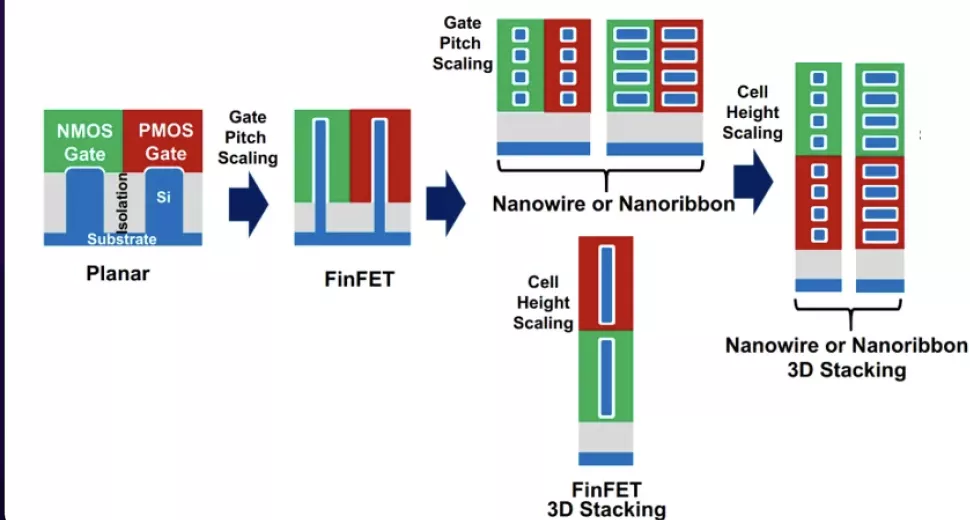

英特尔可能会将目光重新投向晶体管的设计上,以便在2nm或以下先进制程的半导体工艺上使用。最近,一项新的专利似乎指明了英特尔前进的方向,即“堆叠叉片式晶体管(stacked forksheet transistors)”技术,以保持摩尔定律前进的动力。专利并没有提供太多的细节,而且英特尔也没有提供PPA(功率性能面积)的改进数据作为参考。

复旦大学微电子学院周鹏教授团队针对当下系统存算分离的能效瓶颈难题,发现了新型二维铁电半导体在集成电路领域的应用方案,实现了铁电存储计算技术的原始创新,提供了发展存算融合系统的器件范式。

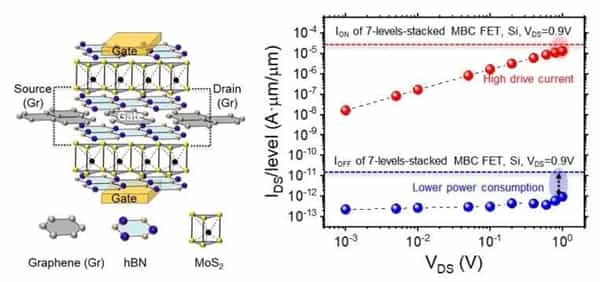

复旦大学微电子学院教授周鹏团队针对具有重大需求的3-5纳米节点晶体管技术,验证了双层沟道厚度分别为0.6 /1.2纳米的围栅多桥沟道晶体管(GAA,Gate All Around),实现了高驱动电流和低泄漏电流的融合统一,为高性能低功耗电子器件的发展提供了新的技术途径。