科学家开发高效3D电子电路制造方法

随着科技的不断进步,电子设备正变得越来越小巧且功能强大,这对内部组件的布局和设计提出了更高的要求。传统平面印刷电路板(PCB)虽然在过去几十年里取得了显著的进步,但在空间利用效率上已经接近极限。科学家开发高效3D电子电路制造方法

随着科技的不断进步,电子设备正变得越来越小巧且功能强大,这对内部组件的布局和设计提出了更高的要求。传统平面印刷电路板(PCB)虽然在过去几十年里取得了显著的进步,但在空间利用效率上已经接近极限。科学家开发高效3D电子电路制造方法

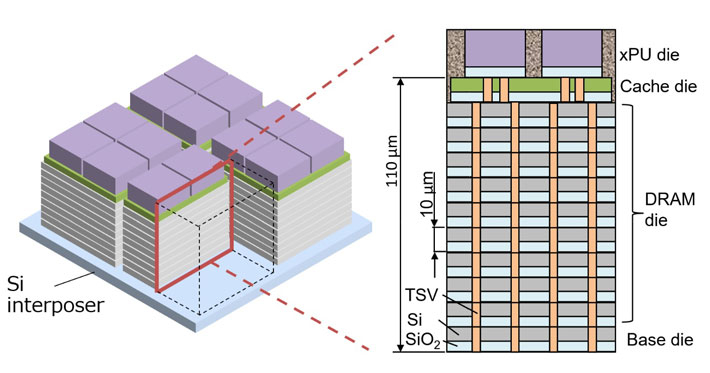

东京工业大学的研究人员报告称,一种处理单元和存储器的三维集成技术实现了全世界最高的性能,为更快、更高效的计算铺平了道路。这种名为“BBCube 3D”的创新堆叠架构实现了比最先进的存储器技术更高的数据带宽,同时也最大限度地减少了位访问所需的能量。

传统集成电路技术使用平面展开的电子型和空穴型晶体管形成互补结构,从而获得高性能计算能力。其密度的提高主要通过缩小单元晶体管的尺寸来实现。例如7nm节点以下业界使用极紫外光刻技术实现高精度尺寸微缩。极紫外光刻设备复杂,在现有技术节点下能够大幅提升集成密度的三维叠层互补晶体管(CFET) 技术价值凸显。然而,全硅基CFET的工艺复杂度高且性能在复杂工艺环境下退化严重。因此,研发与我国主流技术高度兼容的CFET器件与集成,对于自主发展新型集成电路技术具有重要意义。

超越摩尔定律(More than Moore)近几年来在世界级半导体元件会议上占有极重要的研究地位,晶体管尺寸的缩小将面临物理极限的考验,而积层型三维集成电路(monolithic 3DIC)即是其中解决问题最重要的工程技术之一,台湾半导体研究中心(Taiwan Semiconductor Research Institute, TSRI)自2010年开始研究相关技术,是开发前瞻物联网芯片与人工智能芯片的关键技术。