中国研究团队在低维半金属半导体接触研究中取得进展

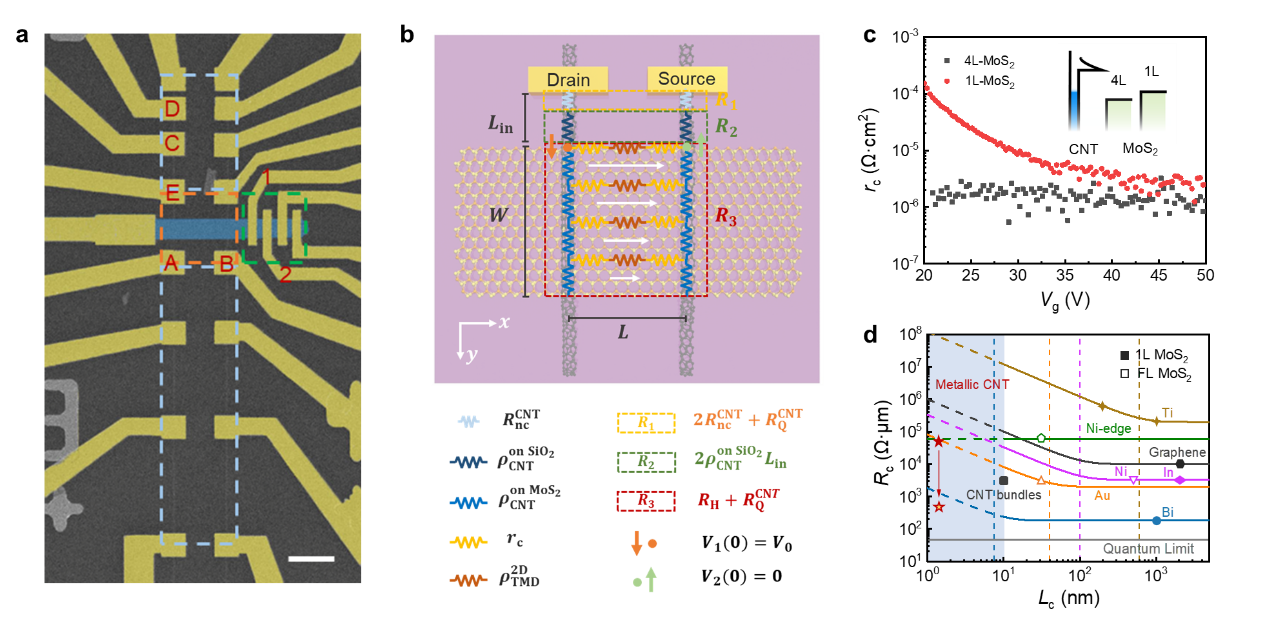

场效应晶体管器件尺寸的极致缩减是半导体集成电路产业发展面临的重要挑战,主要包括沟道长度和接触长度等器件特征尺寸的缩减和性能的优化。受益于超薄的原子结构,新型层状二维半导体具有优异的静电调控能力,在克服短沟道效应、缩减器件沟道长度方面展现出了显著优势。

场效应晶体管器件尺寸的极致缩减是半导体集成电路产业发展面临的重要挑战,主要包括沟道长度和接触长度等器件特征尺寸的缩减和性能的优化。受益于超薄的原子结构,新型层状二维半导体具有优异的静电调控能力,在克服短沟道效应、缩减器件沟道长度方面展现出了显著优势。

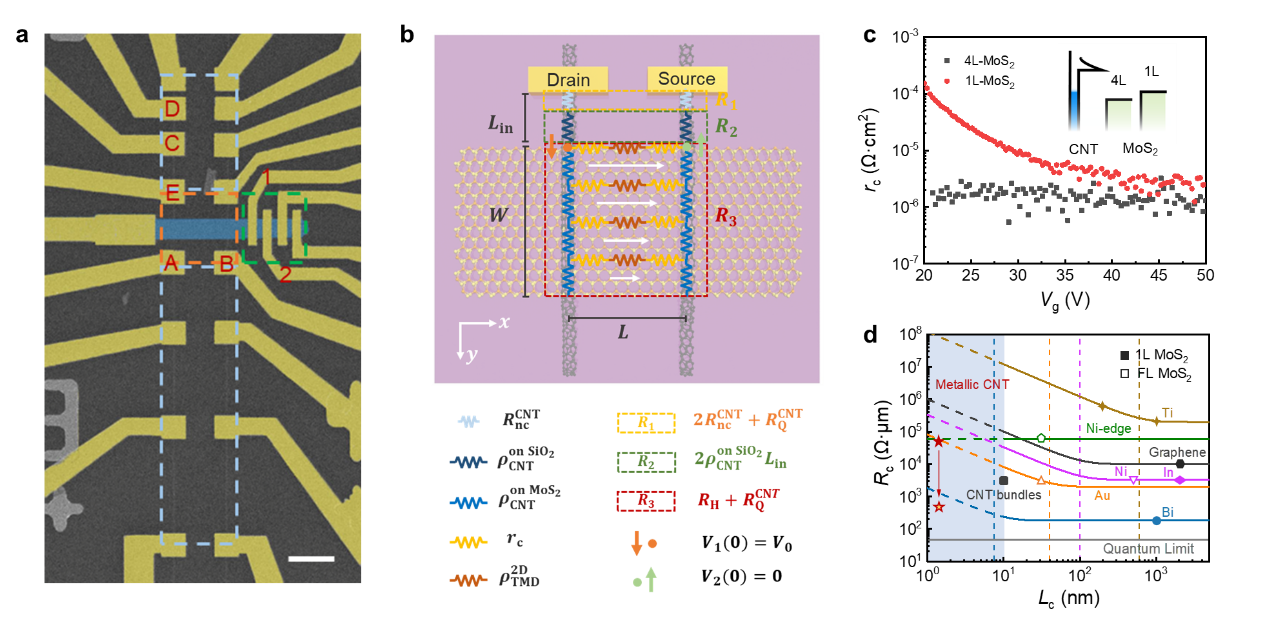

当前MOSFET器件的持续微缩所带来的功耗问题已经成为制约集成电路发展的主要瓶颈。研发新原理器件以突破MOSFET亚阈值摆幅(SS)为60 mV/dec的室温极限,是实现高速度、低功耗CMOS技术和集成电路的重要途径。近年来,包括隧穿晶体管(TFET)、负电容晶体管(NCFET)、冷源晶体管(CSFET)等在内的多种器件技术为实现陡峭亚阈值摆幅和低功耗器件性能提供了思路。

通过铁电栅极绝缘体和原子层沉积氧化物半导体通道,日本科学家制造了三维垂直场效应晶体管,可用来生产高密度数据存储器件。此外,通过使用反铁电体代替铁电体,他们发现擦除数据只需要很小的净电荷,从而提高了写入的效率。发表在2022年IEEE硅纳米电子研讨会上的该项成果,将催生新的更小、更环保的数据存储器。

近日,北京大学化学与分子工程学院彭海琳教授课题组首次报道高迁移率二维半导体表面氧化成高κ栅介质并应用于高性能场效应晶体管器件和逻辑门电路,该研究工作突破了二维高迁移率半导体器件与超薄介电层集成这一瓶颈,有望推动二维集成电路的发展。