中国团队在高性能二维半导体晶体管领域取得重要进展

近日,中国科大微电子学院石媛媛教授课题组设计并实现了一种直接在硅片上制造大规模单层(Monolayer, ML)单晶MoS2高性能晶体管阵列的集成方法,相关研究成果成功入选2024 Symposium on VLSI Technology and Circuits(以下简称VLSI Symposium)。

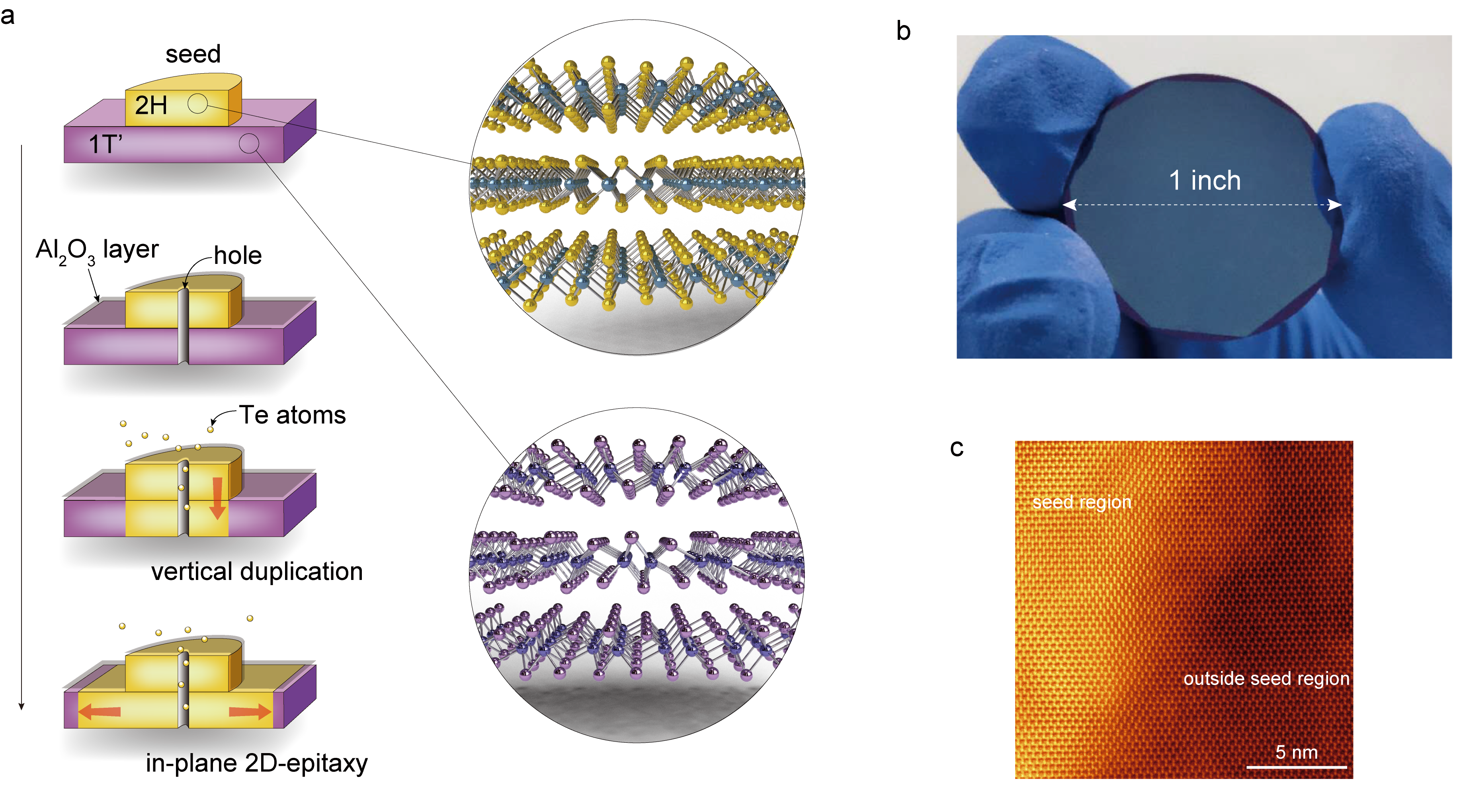

北大团队在二维半导体单晶制备研究中取得重要进展

二维层状半导体材料在具有几个原子层厚度的同时能够保持较高载流子迁移率,因而成为抑制短沟道效应、进一步缩小晶体管尺寸的重要备选材料。然而,目前制备大面积二维半导体薄膜的方法大多采用不同成核点成核、晶畴生长拼接而成。这种方法会在晶畴之间形成晶界,而且不能保证半导体薄膜100%的覆盖率,从而限制了基于这类薄膜制备的器件的性能和均一性。基于大面积集成电路对于半导体器件性能以及均一性的要求,在器件基底上直接制备晶圆尺寸连续二维半导体单晶材料是产业界、科研界亟待解决的科学和技术问题。